Programmable array logic (PAL)

Programmable array logic (PAL) is a large scale integrated programmable logic device that is used for the synthesis of combinational as well as sequential logic. A PAL consists of a programmable AND gate array followed by a fixed OR gate array. This means that the PAL can be programmed to generate the required product terms in the AND gate array but the outputs of the AND gate array are connected in a fixed manner to the different OR gates of the OR gate array. Thus there is no need to find any common product terms between the different output logic functions and all the output functions are synthesized in their

minimum sum of product forms.

Programmable Array Logic (PAL) Devices

The final programmable logic device to be discussed is the Programmable Array Logic or PAL device. The general structure of this device is similar to PLA, but in a PAL device only AND gates are programmable. The OR array in this device is fixed by the manufacturer. This makes PAL devices easier to program and less expensive than PLA. On the other hand, since the OR array is fixed, it is less flexible than a PLA device.

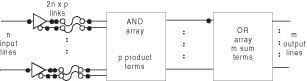

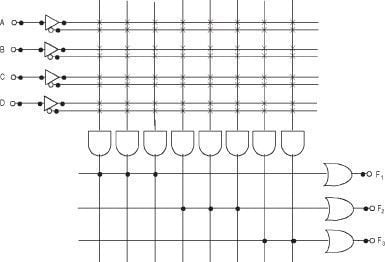

represents the general structure of a PAL device. It has n input lines which are fed to buffers/inverters. Buffers/inverters are connected to inputs of AND gates through programmable links. Outputs of AND gates are then fed to the OR array with fixed connections. It should be noted that, all the outputs of an AND array are not connected to an OR array. In contrast to that, only some of the AND outputs are connected to an OR array which is at the manufacturer's discretion. This can be clarified by Figure 6.23, which illustrates the internal connection of a four-input, eight AND-gates and three-output PAL device before programming. Note that while every buffer/inverter is connected to AND gates through links, F1-related OR gates are connected to only three AND outputs, F2 with three AND gates, and F3 with two AND gates. So this particular device can generate only eight product terms, out of which two of the three OR gates may have three product terms each and the rest of the OR gates will have only two product terms. Therefore, while designing with PAL, particular attention is to be given to the fixed OR array.

No comments:

Post a Comment